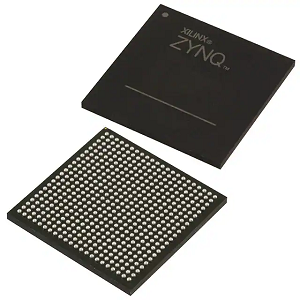

XC7Z015-2CLG485I – Ολοκληρωμένα κυκλώματα (ICs), Ενσωματωμένα, System On Chip (SoC)

Χαρακτηριστικά Προϊόντος

| ΤΥΠΟΣ | ΠΕΡΙΓΡΑΦΗ |

| Κατηγορία | Ολοκληρωμένα κυκλώματα (IC) |

| Mfr | AMD |

| Σειρά | Zynq®-7000 |

| Πακέτο | Δίσκος - σχάρα |

| Κατάσταση προϊόντος | Ενεργός |

| Αρχιτεκτονική | MCU, FPGA |

| Βασικός επεξεργαστής | Διπλό ARM® Cortex®-A9 MPCore™ με CoreSight™ |

| Μέγεθος Flash | - |

| Μέγεθος RAM | 256 KB |

| Περιφερειακά | DMA |

| Συνδεσιμότητα | CANbus, EBI/EMI, Ethernet, I²C, MMC/SD/SDIO, SPI, UART/USART, USB OTG |

| Ταχύτητα | 766 MHz |

| Κύρια Χαρακτηριστικά | Artix™-7 FPGA, 74K Logic Cells |

| Θερμοκρασία λειτουργίας | -40°C ~ 100°C (TJ) |

| Πακέτο / Θήκη | 485-LFBGA, CSPBGA |

| Πακέτο συσκευής προμηθευτή | 485-CSPBGA (19x19) |

| Αριθμός I/O | 130 |

| Βασικός αριθμός προϊόντος | XC7Z015 |

Έγγραφα & Μέσα

| ΕΙΔΟΣ ΠΟΡΟΥ | ΣΥΝΔΕΣΜΟΣ |

| Φύλλα δεδομένων | Προδιαγραφές SoC Zynq-7000 |

| Περιβαλλοντικές Πληροφορίες | Xiliinx RoHS Cert |

| Προτεινόμενο προϊόν | Όλα τα προγραμματιζόμενα SoC Zynq®-7000 |

| Μοντέλα EDA | XC7Z015-2CLG485I από την Ultra Librarian |

Περιβαλλοντικές & Εξαγωγικές Ταξινομήσεις

| ΧΑΡΑΚΤΗΡΙΣΤΙΚΟ | ΠΕΡΙΓΡΑΦΗ |

| Κατάσταση RoHS | Συμβατό με ROHS3 |

| Επίπεδο ευαισθησίας σε υγρασία (MSL) | 3 (168 ώρες) |

| Κατάσταση REACH | REACH Δεν επηρεάζεται |

| ECCN | 3A991A2 |

| HTSUS | 8542.39.0001 |

PL Power-Ενεργοποίηση/Απενεργοποίηση Αλληλουχία τροφοδοτικού

Η συνιστώμενη ακολουθία ενεργοποίησης για το PL είναι VCCINT, VCCBRAM, VCCAUX και VCCO για να επιτευχθεί η ελάχιστη λήψη ρεύματος και να διασφαλιστεί ότι οι I/Os έχουν 3 καταστάσεις κατά την ενεργοποίηση.Η συνιστώμενη ακολουθία απενεργοποίησης είναι η αντίστροφη από τη σειρά ενεργοποίησης.Εάν το VCCINT και το VCCBRAM έχουν τα ίδια συνιστώμενα επίπεδα τάσης, τότε και τα δύο μπορούν να τροφοδοτηθούν από την ίδια τροφοδοσία και να αυξηθούν ταυτόχρονα.Εάν το VCCAUX και το VCCO έχουν τα ίδια συνιστώμενα επίπεδα τάσης, τότε και τα δύο μπορούν να τροφοδοτηθούν από την ίδια τροφοδοσία και να αυξηθούν ταυτόχρονα.

Για τάσεις VCCO 3,3 V σε τράπεζες I/O HR και τράπεζα διαμόρφωσης 0:

• Η διαφορά τάσης μεταξύ VCCO και VCCAUX δεν πρέπει να υπερβαίνει τα 2,625 V για περισσότερο από το TVCCO2VCCAUX για κάθε κύκλο ενεργοποίησης/απενεργοποίησης για να διατηρηθούν τα επίπεδα αξιοπιστίας της συσκευής.

• Ο χρόνος TVCCO2VCCAUX μπορεί να κατανεμηθεί σε οποιοδήποτε ποσοστό μεταξύ των ράμπων ενεργοποίησης και απενεργοποίησης.

Πομποδέκτες GTP (μόνο XC7Z012S και XC7Z015)

Η συνιστώμενη ακολουθία ενεργοποίησης για την επίτευξη ελάχιστης λήψης ρεύματος για τους πομποδέκτες GTP (μόνο XC7Z012S και XC7Z015) είναι VCCINT, VMGTAVCC, VMGTAVTT Ή VMGTAVCC, VCCINT, VMGTAVTT.Τόσο το VMGTAVCC όσο και το VCCINT μπορούν να αυξηθούν ταυτόχρονα.Η συνιστώμενη ακολουθία απενεργοποίησης είναι η αντίστροφη από τη σειρά ενεργοποίησης για να επιτευχθεί η ελάχιστη λήψη ρεύματος.

Εάν δεν πληρούνται αυτές οι συνιστώμενες ακολουθίες, το ρεύμα που αντλείται από το VMGTAVTT μπορεί να είναι υψηλότερο από τις προδιαγραφές κατά την ενεργοποίηση και την απενεργοποίηση.

• Όταν το VMGTAVTT τροφοδοτείται πριν από το VMGTAVCC και το VMGTAVTT – VMGTAVCC > 150 mV και VMGTAVCC < 0,7 V, η λήψη ρεύματος VMGTAVTT μπορεί να αυξηθεί κατά 460 mA ανά πομποδέκτη κατά τη διάρκεια της ράμπας VMGTAVCC.Η διάρκεια της τρέχουσας κλήρωσης μπορεί να είναι έως και 0,3 x TMGTAVCC (χρόνος ράμπας από GND έως 90% του VMGTAVCC).Το αντίστροφο ισχύει για την απενεργοποίηση.

• Όταν το VMGTAVTT τροφοδοτείται πριν από το VCCINT και το VMGTAVTT – VCCINT > 150 mV και VCCINT < 0,7 V, η λήψη ρεύματος VMGTAVTT μπορεί να αυξηθεί κατά 50 mA ανά πομποδέκτη κατά τη διάρκεια της ράμπας VCCINT.Η διάρκεια της τρέχουσας κλήρωσης μπορεί να είναι έως και 0,3 x TVCCINT (χρόνος ράμπας από GND έως 90% του VCCINT).Το αντίστροφο ισχύει για την απενεργοποίηση.

Δεν υπάρχει συνιστώμενη σειρά για προμήθειες που δεν εμφανίζονται.